ABSTRACT

A pipelined

analog-to-digital converter (ADC) architecture suitable for high-speed (150

MHz), Nyquist-rate A/D conversion is presented. At the input of the converter,

two parallel track-and-hold circuits are used to separately drive the sub-ADC of

a 2.8-b first pipeline stage and the input to two time-interleaved residue

generation paths. Beyond the first pipeline stage, each residue path includes a

cascade of two 1.5-b pipeline stages followed by a 4-b “backend” folding ADC.

The full-scale residue range at the output of the pipeline stages is half that

of the converter input range in order to conserve power in the operational

amplifiers used in each residue path. An experimental prototype of the proposed

ADC has been integrated in a 0.18- m CMOS technology and operates from a 1.8-V

supply. At a sampling rate of 150 MSample/s, it achieves a peak SNDR of 45.4 dB

for an input frequency of 80 MHz. The power dissipation is 71 mW.

Index Terms—Analog–digital (A/D) conversion, CMOS analog

integrated circuits, comparators, folding A/D

converters, mixed analog–digital integrated circuits, operational

amplifiers, pipeline processing, switched-capacitor circuits.

INTRODUCTION

CMOS Nyquist-rate

analog-to-digital converters (ADCs) in modern electronic systems tend to fall

in two broad categories: those that operate at very high sampling rates, up to

several gigahertz, with resolution in the range of 4–8 b, and those that

perform conversions at rates of tens of megahertz while providing resolution in

the range of 10–15 b. The very high-speed low-resolution converters find use

primarily in applications such as instrumentation, wideband communications, and

data retrieval from magnetic storage media. Power consumption is rarely a

primary concern in these applications, and the principal challenge is to

achieve a high sampling rate for resolutions that can be readily achieved

within the matching limitations of CMOS technologies. The target applications

for converters providing higher resolution at sampling rates of tens of

megahertz include communication and medical systems, as well as image and video

data acquisition. The challenge here is to achieve a high resolution in the

presence of component mismatch, thermal noise, and circuit nonlinearity.

The ADC introduced in this work targets

performance between the two categories noted above, namely, a sampling rate of

150 MSample/s and a resolution of 8 bits. These specifications are typically appropriate

for high-speed wireline and wireless communications. For example, the

1000BASE-T Ethernet protocol requires a conversion rate of 125 MSample/s and a

resolution of 7–9 bits, depending on the overall system architecture. Since

four converters must be integrated in a single transceiver, power consumption

becomes an important consideration. For the IEEE 802.11a/g wireless LAN

protocol, ADCs with conversion rates of the order of 80 MSample/s are required,

also with resolution in the range of 7–9 bits. Here, power consumption is of

paramount importance when the target application is portable systems.

The low-power ADC described in this paper

utilizes a combination of architectural concepts and circuit techniques to

achieve the target performance while dissipating only 71 mW of power from a

1.8-V supply. Chapter II provides a detailed overview of the converter

architecture and reviews the choices made to minimize the power dissipation.

Chapter III describes the design of the circuit blocks that have been used to

accommodate low-voltage operation. Chapter IV presents measured results for the

experimental prototype.

CONVERTER ARCHITECTURE

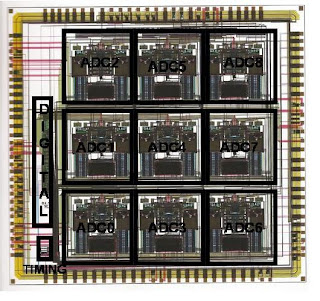

Fig. 2.1 offers a detailed view of the ADC architecture. The input

track-and-hold network is actually “split” into two parallel track-and-hold

circuits, TH1 and TH2, both of which are clocked at the full conversion rate

(150 MHz) and sample the input at nominally identical instances in time. TH1

drives the analog residue generation paths, while TH2 drives the six

comparators comprising the sub-ADC of the 2.8-b first stage of the pipeline. A

2.8-b first stage was chosen to minimize the power and area required for the

overall converter. The track-and-hold function at the input of the converter is

split so as to combat the coupling of kickback noise from the first-stage

sub-ADC comparators into the sensitive residue generation paths, in a manner

similar. Since the six comparators

comprising the sub-ADC in the first pipeline stage are compact, fast, low power

latches without preamplification, their operation creates noise at the level of

several tens of millivolts. With the proposed arrangement, noise from the

operation of the comparators does not degrade the quality of the analog input

signal used for residue generation since the outputs of TH1 and TH2 are

isolated from each other during the hold mode.

As is also shown in Fig. 2.1, residue generation is split into two

paths, A and B, in the first pipeline stage. Each path comprises a sampling

network (not shown explicitly), a 2.8-b DAC, a subtractor and an interstage

gain of 2. These functions are performed by a switched-capacitor network that

is described in detail in Section III. The two residue generation paths operate

at half the conversion rate (75 MHz) and in antiphase; that is, when path A

samples the output of TH1, path B amplifies its held input. Time- interleaving

the operation of two residue paths results in significant savings in power.

Most of the power in each path is dissipated by the operational amplifiers used

for residue generation, and the use of two paths operating at 75 MHz results in

nearly a factor of two reduction in power consumption compared to a single path

operating at the full conversion rate of 150 MHz. The first-stage sub-ADC

operates at the full rate of the converter, and its decisions are routed to

each of the two residue generation paths with the use of an appropriate digital

switch.

The gain in each of the first-stage residue paths is 2, rather

than a gain of 4 that would typically be used for a pipeline stage providing

two bits of encoding. Thus, instead of maintaining a full-scale range for the

residue output that is the same as that of the analog input to the stage, the

output range is scaled by a factor of 2. Specifically, while the differential

full-scale range of the input is 1.6Vpp, the differential range of the residue

is 0.8Vpp. This “scaling” of the signal range facilitates a substantial

reduction in the power dissipated by the operational amplifiers used for

residue generation.

The ideal transfer characteristic of the 2.8-b pipeline stage,

also known as a “3-b stage with digital error correction”, is shown in Fig.

2.2. The stage resolves 2 bits of the conversion using six, rather than three, comparators.

This allows for the compensation of large comparator offsets, as shown in Fig.

2.2. For this design, comparator offsets as large as 100 mV can be tolerated in

the first pipeline stage.

For each residue path emanating from the first stage, a cascade of

two additional 1.5-b pipeline stages is used to encode the next two most

significant bits. These stages employ two comparators each and an interstage

gain of 2. Therefore, the differential full-scale range of the residue output

of each pipeline stage is maintained at 0.8Vpp. For the described arrangement

of interstage gains, the step size at the converter input corresponding to one

LSB is 6.25 mV, while at the outputs of the first three pipeline stages it is

12.5, 25, and 50 mV, respectively.

After digital error correction, the first three stages of the

converter pipeline provide the four most significant bits (MSBs) of the conversion.

In each residue path a 4-b flash stage follows the three pipeline stages to

encode the four least significant bits (LSBs), for a total of 8 bits. The

“backend” 4-b stage uses a simple folding technique as described in Section

III. All comparator outputs for this architecture are fed to a decoding and

error-correction block that generates the final 8-b digital output. This

digital-logic block can be easily realized in dedicated hardware or with a

digital signal processor.

CIRCUIT DESIGN AND

IMPLEMENTATION

The two track-and-hold circuits at the input of the

converter are implemented in a pseudodifferential fashion, while all of the

remaining analog blocks are fully differential circuits. All of the circuits

are powered from a 1.8-V supply.

Fig.

3.1.1 shows a single-ended schematic of the circuit used to implement both of

the track-and-hold networks. TH2 is a scaled version of TH1. The track-and-hold

network comprises Fig. 3.1.1. Track-and-hold network. a sampling switch MSW

with an associated bootstrapping network, a hold capacitor CH, and a

source-follower buffer. Capacitor represents the sampling capacitance of the

residue generation network for either path A or B, whichever is sampling the

output of TH1 on a given cycle. For TH2, CL represents the sampling

capacitance at the combined input of the six sub-ADC comparators.

The bootstrapping

network in Fig. 3.1.1 resembles the one described. During the tracking phase

Φ1, switches M6 and M7 conduct, and the voltage on the

bootstrap capacitor CB is applied between the gate and source of the

sampling switch. Therefore, VGS for the sampling switch remains

approximately constant for varying input voltages. This in turn gives rise to a

constant resistance for the sampling switch during track mode, which improves

the linearity of the sampling network. During the hold phase Φ, switches M6

and M7 are off and transistor conducts, turning off the sampling

switch MSW. The sampled input voltage is thus held on CH.

During the same phase, switches M8 and M9 conduct,

charging the bootstrap capacitor CB to a bias voltage VB

of about 1.3 V.

The principal difference between this

implementation and that described is that the bias voltage VB is

less than the supply voltage VDD. As a result, although during the

tracking mode the voltage at the top plate of CB is allowed to go

above VDD, it still remains low enough to avoid introducing

long-term reliability concerns associated with voltage stress on the sampling

switch during transients. As a further precaution, the connection for the

inverter that drives M7 is made to the bottom plate of CB,

the body of M7 is connected to its source, and transistor M5

is used as a cascode to M4.

Transistor M1 in Fig. 3.1.1 is a PMOS

source follower with its body connected to its source. Therefore, the gain from

its gate to the source is nearly unity. Transistor M2 serves as a current

source to bias M1. The use of this simple source follower as a

buffer is well suited to low-voltage operation with the full-scale voltage

range of 0.8 Vpp at each of the differential inputs. As the input voltage

changes, the variation in VDS for M1 and M2

causes a “compression” of the output voltage for large signal excursions,

leading to third-order distortion in the differential output. Buffers such as

this have been used extensively in converters requiring only 6-b linearity and

recent results suggest that the topology may be suitable for achieving

linearity as high as 10 bits. Simulations and the observed performance of the

experimental prototype indicate that the linearity achieved with this sampling

network is approximately 9 bits.

Switch MSW in the track-and-hold circuit

should be as small as possible while still providing sufficient bandwidth to

transfer the highest input frequencies of interest ( 70 MHz). Its small size

guarantees minimal charge injection (fraction of an LSB) into CH.

Clock jitter of approximately 4 ps can be tolerated in the sampling switches.

3.1.2 depicts the output of the track-and-hold networks before and after

the sampling instance, which is denoted by t0. Owing to the time

interleaving, during a given conversion cycle, either residue path A or B

samples the output of TH1 at time , which also marks the end of the hold phase

for the track and hold networks. The first-stage comparators begin resolving

the output of TH2 at an intermediate time t1 between t0

and t2.

As shown in

Fig. 3.1.2, immediately after sampling, there is a transient at the

track-and-hold output. The tail of this transient may result in a difference of

as much as 30 mV between the voltage encoded by the first-stage sub-ADC and the

voltage sampled by the residue paths. This transient is not the result of

potentially nonlinear second-order effects during sampling, such as sampling

switch charge injection, but is rather due solely to the linear behavior of the

sampling network and the source follower buffers. The origin of the transient

is explained in detail in the Appendix, where (A14) indicates that the maximum

magnitude of the transient can be as large as 11% of the input full-scale

range. The resulting difference in the voltage encoded by the sub-ADC and that

used between the analog residue paths must be taken into account when budgeting

the total offset for the comparators of the first stage.

The simple

track-and-hold circuits used here are linear enough to achieve the desired

resolution while offering a significant power savings compared to those that

are based on the use of an operational amplifier in a feedback network. The

power in the track-and-hold networks is largely that consumed for biasing the

source followers, and there are no power-demanding auxiliary circuits; the

bootstrap network dissipates negligible power.

First-Stage Comparators

Fig. 3.2.1 shows a circuit diagram for the

comparators used in the first-stage sub-ADC. Each of the six comparators

comprises a regenerative core preceded by a switched-capacitor network that

establishes its equivalent reference voltage. Input voltages Vin1

and Vin2 correspond to the two outputs of the pseudodifferential

track-and-hold network TH2. The timing diagram in Fig. 3.2.2 shows the clock

phases Φ1 and Φ2 used to control the operation of the

comparators. The sampling clock and clock are used to control the timing in the

analog residue paths.

During phase Φ1, reference voltages +Vref and –Vref

(where Vref=0.4) are sampled onto capacitors CS1 and CS2,

as shown in Fig. 3.2.1. During phase Φ1, the output of TH2 is

applied on both capacitors.

Capacitor ratios (CS1/CS2) of 3/13, 5/11, 7/9and

their inverses are used for the six comparators to establish the necessary

equivalent differential references.

Also during phase Φ1, the PMOS switch Mbias

in the regenerative core is activated and bias current flows through the latch.

However, regeneration begins later, with the onset of phase Φ2, when

switch Mreg is turned off. It can be shown analytically that

establishing current flow in the latch well before initiating regeneration

significantly reduces the latch’s dynamic input-referred offset.

The comparator dissipates approximately 0.5 mW of

power when operating at 150 MHz and exhibits 3σ a static offset of about 36 mV.

This offset value has been estimated with simulations using typical technology

parameters for transistor mismatch. The six comparators are allowed to

regenerate for about 0.75 ns, while φ2 is low. After regeneration is discontinued,

the resulting outputs are amplified and stored in set-reset (SR) latches, not

shown in Fig. 3.2.1.

For the

first-stage architecture shown in Fig. 1.1, Table 3.2.1 summarizes the main

factors contributing to a difference between the equivalent voltage encoded by

the first-stage sub-ADC and that sampled by a residue generation path. The

approximate worst-case magnitudes of these contributions as referred to the

input of the overall ADC are included in Table 3.2.1. These differences can be

treated as added comparator offset for the firststage sub-ADC and are well

tolerated, provided that all sources of mismatch remain within the correctable

range of 100 mV mentioned in Section II. An explanation of the various

contributions follows.

In addition

to static offsets in the comparators, there may exist a settling error with

respect to the final values of the reference voltages sampled on CS1

and CS2 in Fig. 3.2.1. Also, since the comparators regenerate for a

limited time, there may not be enough time for an input voltage that lies

within 5 mV of the equivalent reference of one of the comparators to be

resolved correctly. Other error contributions result from mismatch between the

two track-and-hold networks. A static mismatch may exist between TH1 and TH2.

Also, TH1 and TH2 may not sample at precisely the same instance due to sampling

clock propagation delay. This time difference would translate to a sampled

value offset for a time-varying input waveform. In the layout of the

experimental prototype, the sampling switches for the two track-and-hold

networks are placed next to each other to minimize any sampling time

differences. Finally, there is the offset component due to the transients at

the output of the track-and-hold networks, as described in Section III-A. In a

worst-case scenario, all of these offset contributions add up to a total of

about 85 mV, therefore leaving a healthy margin to the maximum correctable

range of 100 mV.

Residue Generation Paths

Fig. 3.3.1 is a schematic of the switched-capacitor

network used for each of the residue generation paths in the first pipeline

stage. Although the residue paths are implemented as fully differential

circuits, a single-ended version is shown in Fig. 3.3.1 for clarity. A total

sampling capacitance CS1 is divided into eight equal capacitors.

During phase φ3, for one of the two residue paths, the output of TH1, denoted

as Vin1 in Fig. 3.31, is sampled onto all eight sampling capacitors.

At the same time, the input and output of the op amp are held at the

common-mode voltage VCM. During phase φ3, reference voltages +Vref

and –Vref are applied on the two “outermost” sampling capacitors in

Fig. 3.3.1, respectively. During this same phase, the decision of the six

comparators of the first-stage sub-ADC controls whether +Vref or –Vref

is applied to the remaining six sampling capacitors. The subtraction of the

charge sampled on the sampling capacitors during φ3 from the charge that was

sampled on them during φ3 corresponds to the subtraction of the DAC output from

the output of TH1 depicted in Fig. 1.1. The feedback capacitance CF

is half the total sampling capacitance CS, thus realizing a

closed-loop gain of 2.

For stages 2

and 3 in each residue path, the residue generation network is very similar to

that shown in Fig. 3.3.1. However, in this case, the sampling capacitance is

divided into only four equal capacitors, and the polarity of the references for

two of them is controlled by the two comparators that form the sub-ADC in each

1.5-b stage. The comparators employ the same topology as those in the first

stage, shown in Fig.3.2.1, and are driven by the output of the preceding stage

through a simple preamplifier that reduces kickback noise.

Sampling

capacitor sizes for stages 1–3 were conservatively set to 1.6, 1.2, and 1 pF,

respectively.

Operational Amplifier

A schematic of the operational amplifier topology

used for residue generation in all stages of the pipeline is shown in Fig.

3.4.1. Capacitors marked CN in Fig. 3.4.1 are used to partially

neutralize the gate-to-drain capacitance of input transistors M1 and

M2, thereby increasing the circuit’s bandwidth. Common-mode feedback

is provided by means of a switched-capacitor network.

As noted in

Section II, for the residue output of every pipeline stage, a full-scale

differential range of only 0.8Vpp is used in order to conserve power. Given the

0.8-V differential full-scale range, the voltage range at each of the two

amplifier outputs is 0.4Vpp. This small voltage range is acceptable since the

signal-to-noise ratio (SNR) of this converter is limited by quantization rather

than thermal noise. The differential output of the amplifier is reset to zero

during the sampling phase by resetting the two outputs to the middle of their

0.4-Vpp range. Thus, during amplification, the maximum voltage excursion at

either of the two outputs is 200 mV.

At the

beginning of the amplification phase, voltage “spikes” are induced at the

inputs of the operational amplifier. As charge redistributes between the

sampling and feedback capacitors, these voltage spikes decay exponentially to a

value close to zero, while at the same time the op amp outputs settle to their

final values. For a closed-loop gain of 2 in every stage, the maximum magnitude

of the voltage spike at any of the op amp inputs is no more than 100 mV. An

example of the voltage response at one of the inputs and one of the outputs of

the op amp during the amplification phase is shown in the inset of Fig. 3.4.1.

The magnitude of the initial spike at the input is within the linear range of

the input differential pair and therefore too small to cause slewing at the op amp

output or drive any of the op amp transistors, including current sources M0,M3,M4,M9

and M10, out of saturation. Thus, there are no long voltage

transients due to slewing or to bias current recovery that affect the response

of the op amp during the amplification phase. The absence of such transients

obviates the need for large currents in transistors M7, M5,

M3 and M8, M6, M4 the cascade

branches of the amplifier. As a result, only 320 A of bias current is needed in

these devices.

The low bias currents in the casocde branches are

sufficient to drive the output capacitive load, and their small value has two

beneficial effects. First, it reduces the power consumed by the op amp to only

5.11 mW. This is approximately 35% less than the typical case where the currents

in the cascade branches are comparable to those flowing in the input devices, M1

and M2. Second, the small current through M7, M5,

M3 and M8, M6, M4 results in a

large output resistance for the cascode transistors, corresponding to a high op

amp gain. The amplifier provides an open-loop gain of 80 dB over the entire

differential output range.

The only

drawback of the low currents in the cascade branches is a relatively low value

of gm for cascode transistors M7 and M8, which

translates to a low nondominant pole for the amplifier. This is reflected in

the unity-gain bandwidth of the op amp, which is only 400 MHz. During the

amplification phase, the feedback factor for the closed-loop configuration is

at most 14 dB, and the phase margin for that feedback factor is about 60.

Since the

settling requirements are more relaxed in the second and third stages, the op

amps for those stages are biased at a lower current.

“Backend” 4-B ADC

A schematic of the 4-b backend ADC used in each

path is shown in Fig. 3.5.1. A coarse sign comparator makes an early decision

as to the polarity of its differential input voltage while the input is still

settling. After the input has settled, its magnitude is encoded by a 3-b flash

ADC. The threshold voltages for the 3-b flash ADC are provided by a

differential reference ladder, with their polarity (positive or negative)

determined by the result of the coarse sign comparison, as shown in Fig. 3.5.1.

For positive input voltages, the polarity of the reference voltages that set

the thresholds in the 3-b flash ADC is positive, while the opposite is true for

negative inputs, as indicated by the stage’s transfer characteristic in Fig.

3.5.2.

Also included in the backend ADC is a “fine” sign

comparator, as shown in Fig. 3.5.1. After the input voltage has settled, this

comparator makes an accurate determination of the sign of the input, which is

important for the case when the input voltage lies within ±1LSB of the

threshold in the middle of the input range. With this configuration, it is

possible that the decisions of the coarse and fine sign comparators are not

identical.A typical such situation is depicted in Fig. 3.5.3. The input voltage

to the stage experiences a small initial “peak” caused by transients in the

settling of the switched-capacitor network of the preceding pipeline stage

during the amplification phase. Moreover, the coarse comparator may also

exhibit an offset. As shown in the figure, the decisions of the coarse and fine

comparators can thus be different. If the input settles to a final value with a

magnitude of less than 50 mV (corresponding to the LSB step size for this

stage), the discrepancy is of no consequence since none of the thresholds of

the 3-b flash ADC are ever be reached by an input of such small magnitude,

regardless of whether it is positive or negative. For an input to the stage

with a final value of magnitude larger than 50 mV, the input, as it settles,

quickly moves away from the center region of the input range. Provided that the

offset of the coarse sign comparator is no more than 50 mV, the decisions of

the two sign comparators will then match. The realization of this last scenario

was extensively examined via simulations. If there is concern that the two sign

comparators may still make different decisions for an input more than ±1LSB

from the center, additional comparators need to be used.

Each of the comparators comprising the flash ADC in

Fig. 3.5.1, as well as the fine sign comparator, includes two preamplifiers

with an intermediate input-output offset cancellation network. These

comparators in the final stage are responsible for the LSB transitions of the

overall converter. They are preceded by a total gain of only 8 (three pipeline

stages, each with an interstage gain of 2. Therefore, offset cancellation for

the comparators is necessary to ensure that the target DNL performance can be

achieved.

With the architecture shown in Fig. 3.5.1, the

backend ADC can encode the 4 LSBs using only nine comparators, instead of the

usual 15 required for a 4-b flash ADC.

CMOS Switches

The CMOS switches used in the switched-capacitor

networks are shown in Fig. 12. When such a switch is conducting, the body of

the PMOS device is connected to its source. Because of the absence of body

effect, the resistance of the switch is lowered, especially near the middle of

the voltage range, where the switch resistance is highest. When the switch is

off, the body of the PMOS device is connected to the highest voltage present (VDD)

to ensure that the drain-to-bulk and source-to-bulk diodes for this device are

always reverse biased for any voltage levels between ground and VDD

on either side of the switch. This arrangement lowers the peak resistance of

the switch during conduction by about 50% compared to the case where the body

of the PMOS transistor is permanently connected to VDD. The

reduction in resistance in turn allows a reduction in the size of the switches

and their associated parasitic loading on the switched-capacitor network that

employs them. Since the capacitance of the n-well of the main PMOS transistor

in the switch to the substrate is small, the devices used to switch the body of

the main PMOS transistor are approximately 16 times smaller than the PMOS

transistor itself.

CONCLUSION

A 150-MSample/s, 8-b, low-power ADC based on a pipeline

architecture has been described. Two open-loop track-and-hold circuits are used

to isolate the sensitive residue path from the noisy inputs to the comparators

of the first pipeline stage. The use of two time-interleaved residue paths in

the first and subsequent stages saves power relative to a single path operating

at the full conversion rate. Since both residue paths are driven from the same

track-and-hold circuit, no distortion is introduced by timing mismatch between

the time-interleaved paths. Signal scaling is used to facilitate the use of a

low-power, high-speed, high-gain op amp. A simple folding technique is used in

the final 4-b stage to reduce the number of comparators needed.

The

experimental prototype chip dissipates 71 mW, which represents the lowest power

consumption reported to date for a CMOS, full-Nyquist, 150-MSample/s, 8-b

converter that does not require calibration.

No comments:

Post a Comment

leave your opinion